#### VLSI CAD ENGINEERING

GRACE GAO, PRINCIPLE ENGINEER, RAMBUS INC.

AUGUST 5, 2017

Õ

0

$\bigcirc$

#### Agenda

- · CAD (Computer-Aided Design)

- General CAD

- CAD innovation over the years (Short Video)

- VLSI CAD (EDA)

- EDA: Where Electronic Begins (Short Video)

- Zoom Into a Microchip (Short Video)

- Introduction to Electronic Design Automation

- Overview of VLSI Design Cycle

- VLSI Manufacturing

- Intel: The Making of a Chip with 22nm/3D (Short Video)

- EDA Challenges and Future Trend

- VLSI CAD Engineering

- EDA Vendors and Tools Development

- Foundry PDK and IP Reuse

- CAD Design Enablement

- CAD as Career

- Q&A

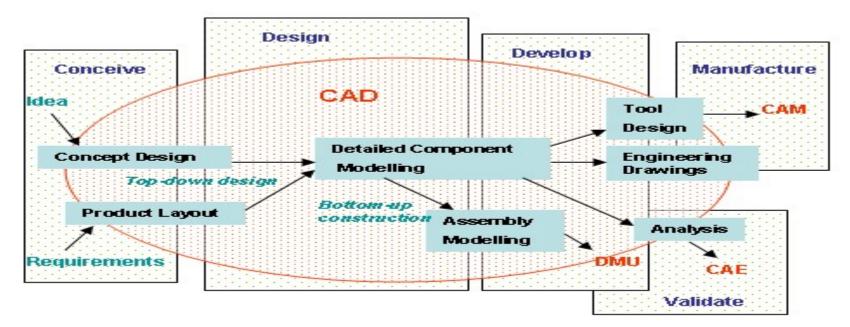

### CAD (Computer-Aided Design)

#### General CAD

Computer-aided design (CAD) is the use of <u>computer systems</u> (or <u>workstations</u>) to aid in the creation, modification, analysis, or optimization of a <u>design</u>

#### CAD innovation over the years (Short Video)

• <u>https://www.youtube.com/watch?v=ZgQD95NhbXk</u>

#### CAD Tools

#### Commercial

- Autodesk <u>AutoCAD</u>

- CAD International <u>RealCAD</u>

- Autodesk Inventor

- Bricsys <u>BricsCAD</u>

- Dassault <u>CATIA</u>

Dassault <u>SolidWorks</u>

- Dassault <u>Solid Works</u>

Kubotek KeyCreator

- Kubotek <u>Reycre</u>

Siemens NX

- Siemens Solid Edge

- PTC <u>PTC Creo</u> (formerly known as Pro/ENGINEER)

- Trimble <u>SketchUp</u>

- AgiliCity Modelur

- <u>TurboCAD</u>

- IronCAD

- MEDUSA

- ProgeCAD

- <u>SpaceClaim</u>

- PunchCAD

- Rhinoceros 3D

- VariCAD

- VectorWorks

- <u>Cobalt</u>

- Gravotech <u>Type3</u>

- RoutCad <u>RoutCad</u>

- <u>SketchUp</u>

- Freeware and open source

- <u>123D</u>

- LibreCAD

- FreeCAD

- BRL-CAD

- OpenSCAD

- NanoCAD

- <u>QCad</u>

- CAD Kernels

- Parasolid by Siemens

- ACIS by Spatial

- <u>ShapeManager</u> by Autodesk

- Open CASCADE

- C3D by C3D Labs

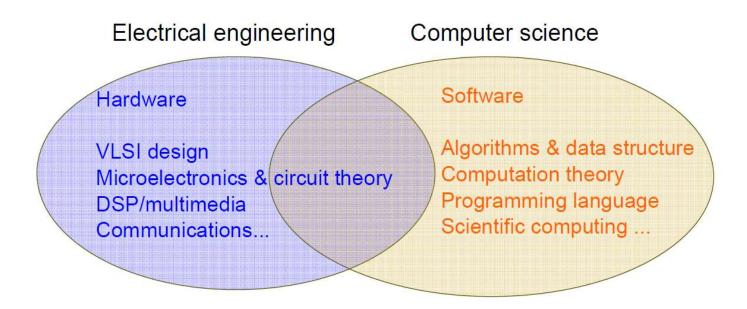

#### VLSI CAD (EDA)

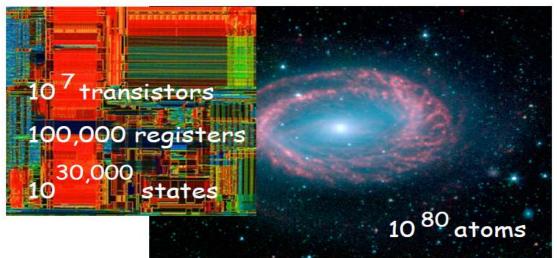

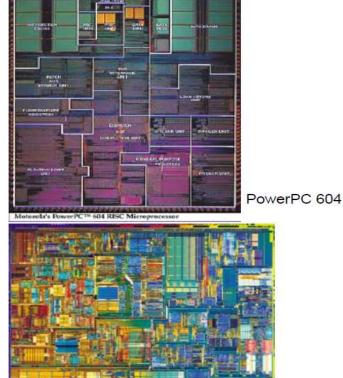

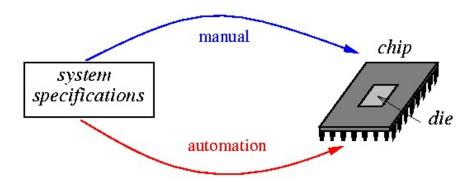

- Very-large-scale integration (VLSI) is the process of creating an integrated circuit (IC) by combining hundreds of thousands of transistors into a single chip.

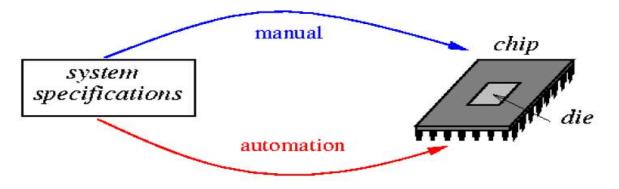

- The design of VLSI circuits is a major challenge. Consequently, it is impossible to solely rely on manual design approaches. Computer Aided Design (CAD) is widely used, which is also referred as electronic design automation (EDA).

#### EDA: Where Electronic Begins (Short Video)

• <u>https://www.youtube.com/watch?v=8uj81PWHImk</u>

#### Zoom Into a Microchip (Short Video)

• <u>https://www.youtube.com/watch?v=Fxv3JoS1uY8</u>

## Introduction to Electronic Design Automation

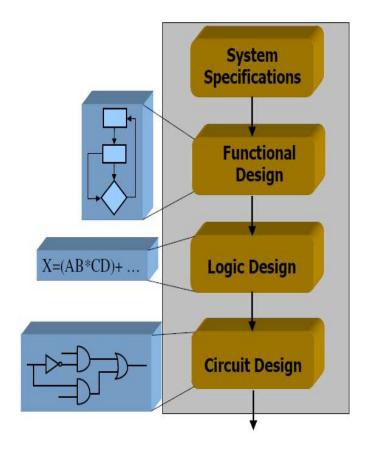

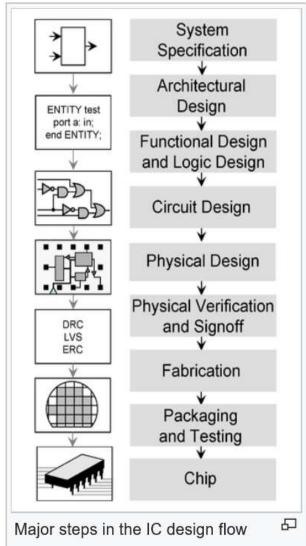

#### Overview of VLSI Design Cycle

Continue from the left **Physical Design** Fabrication Packaging

#### 7 Major Steps in IC Design Flow

- 1. System specification

- 2. Functional design

- 3. Logic synthesis

- 4. Circuit design

- 5. Physical design and verification

- 6. Fabrication

- 7. Packaging

- Other tasks involved: testing, simulation, etc.

- Design metrics: area, speed, power dissipation, noise, design time, testability, etc.

- Design revolution: interconnect (not gate) delay dominates circuit performance in deep submicron era.

- Interconnects are determined in physical design.

- Shall consider interconnections in early design stages.

#### Step 1: System Specification

This is the crucial step as it will affect the future of the product. Here, vendors may want to get feedback from potential customers on what they are looking for

- Instruction set

- Interface (I/O pins)

- Organization of the system

- Functionality of each unit in the system, and how to communicate it to other units.

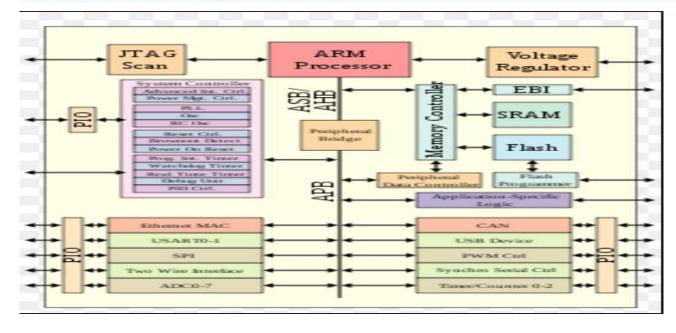

#### Step 2: Architectural Design

This is where the main work starts. With the help of the specification sheet the target IC's architecture is decided and a layout for same is created by design engineers using EDA tools.

# Step 3: Functional and Logic Design Synthesis: Verilog → Gates

Gate Library

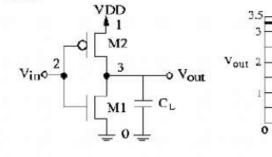

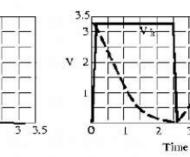

#### Step 4: Circuit Design

M1 3 2 0 0 nch W=1.2u L=0.6u AS=2.16p PS=4.8u AD=2.16p PD=4.8u M2 3 2 1 1 pch W=1.8u L=0.6u AS=3.24p PS=5.4u AD=3.24p PD=5.4u CL 3 0 0.2pF

1

2

Vin

VDD 1 0 3.3

VIN 2 0 DC 0 PULSE (0 3.3 Ons 100ps 100ps 2.4ns 5ns)

.LIB '.. /mod\_06' typical

.OPTION NOMOD POST INGOLD=2 NUMDGT=6 BRIEF .DC VIN OV 3.3V 0.001V .PRINT DC V(3) .TRAN 0.001N 5N .PRINT TRAN V(2) V(3) .END

5

ns

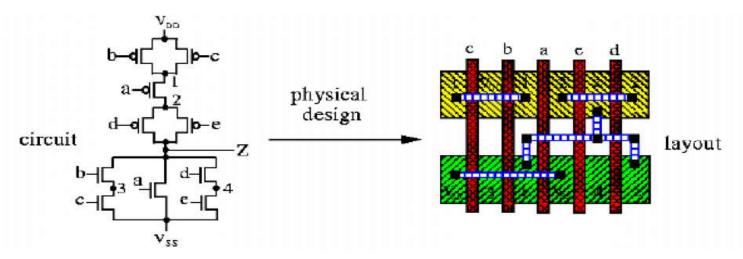

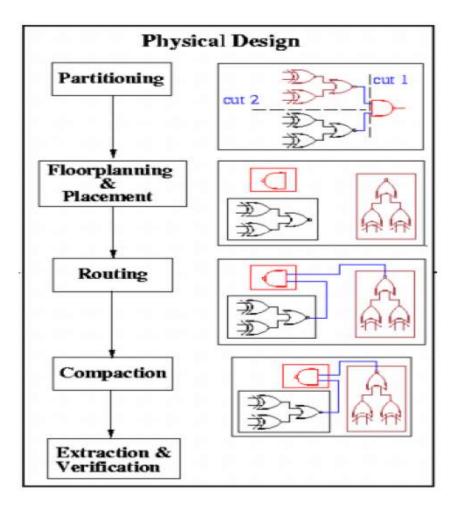

#### Step 5-1: Physical Design

- Physical design converts a circuit description into a geometric description.

- The description is used to manufacture a chip.

- Physical design cycle:

- 1. Logic partitioning

- 2. Floorplanning and placement

- 3. Routing

- 4. Compaction

Others: circuit extraction, timing verification and design rule checking

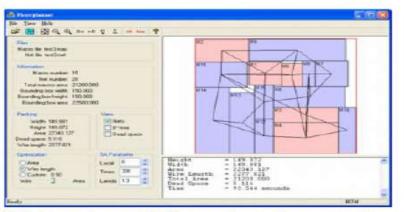

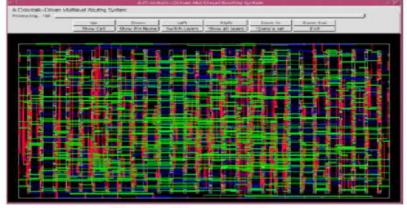

#### Example: Physical Design (Place & Route)

#### B\*-tree based floorplanning system

A routing system

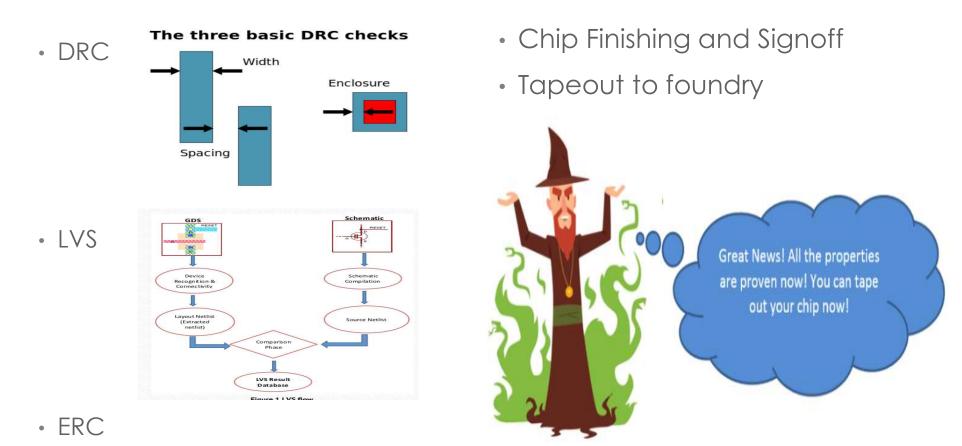

#### Step 5-2: Physical Verification and Signoff

#### VLSI Manufacturing (Coming Step 6 and 7)

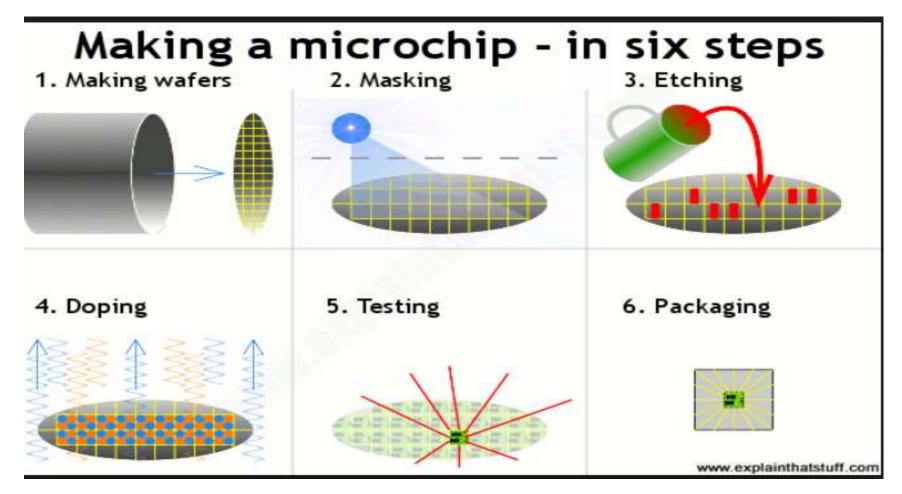

#### Step 6: Fabrication

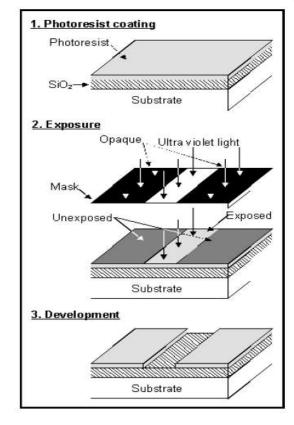

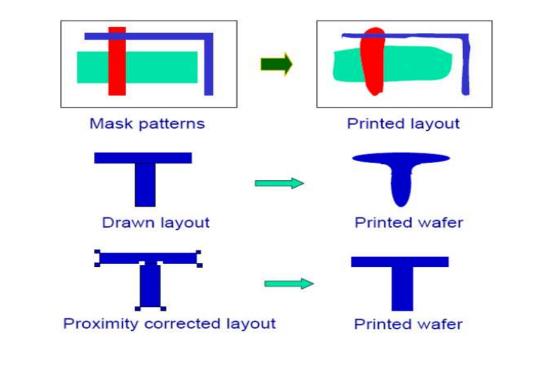

- After layout and verification, the design is ready for fabrication (called tapeout).

- Layout data is converted into photo-lithographic masks.

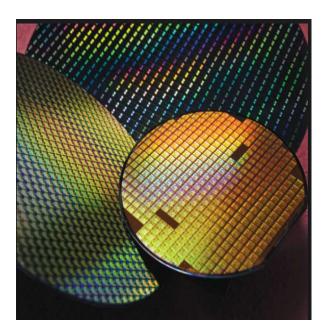

#### Step 7: Packaging and Testing

- After fabrication, each die is tested.

- The wafer is diced into individual chips.

- Each chip is packaged and tested.

#### Intel: The Making of a Chip with 22nm/3D (Video)

https://www.youtube.com/watch?v=d9SWNLZvA8g

#### EDA Challenges and Future Trend

- Several conflicting considerations:

- Design complexity: large number of devices/transistors

- Performance: optimization requirements for high performance

- Time-to-market: about a 15% gain for early birds

- Cost: die area, packaging, testing, etc.

- Others: power, signal integrity (noise, etc), testability, reliability, manufacturability, etc.

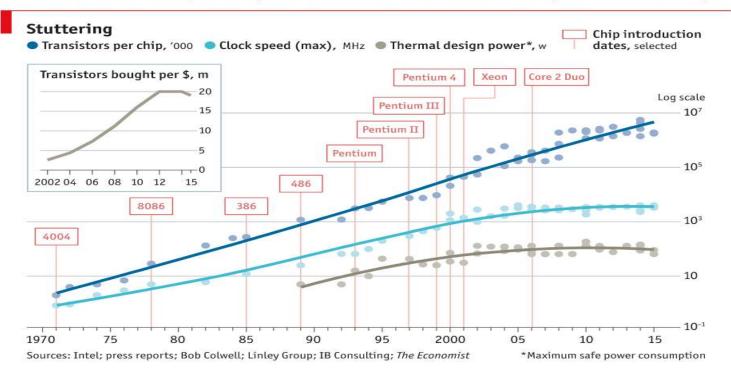

#### Moore's Law: Driving Technology Advances

Logic capacity doubles per IC at a regular interval

- Moore: Logic capacity doubles per IC every two years (1975)

- D. House: Computer performance doubles every 18 months (1975)

#### Technology Roadmap for Semiconductors

| Year                    | 1997    | 1999       | 2002      | 2005    | 2008    | 2011    | 2014      |

|-------------------------|---------|------------|-----------|---------|---------|---------|-----------|

| Technology              | 1000    | 17723424   | 5 5 5     | 10000   | 120     |         |           |

| node (nm)               | 250     | 180        | 130       | 100     | 70      | 50      | 35        |

| On-chip local           |         |            |           |         |         |         |           |

| clock ( $GHz$ )         | 0.75    | 1.25       | 2.1       | 3.5     | 6.0     | 10      | 16.9      |

| Microprocessor          |         |            |           |         |         |         |           |

| chip size $(mm^2)$      | 300     | 340        | 430       | 520     | 620     | 750     | 901       |

| Microprocessor          |         |            |           |         |         |         |           |

| transistors/chip        | 11M     | 21M        | 76M       | 200M    | 520M    | 1.40B   | 3.62B     |

| Microprocessor          |         |            |           |         |         |         |           |

| cost/transistor         | 3000    | 1735       | 580       | 255     | 110     | 49      | 22        |

| (×10 <sup>-8</sup> USD) |         |            |           |         |         |         |           |

| DRAM bits               |         |            |           |         |         |         |           |

| per chip                | 256M    | 1 <b>G</b> | 4G        | 16G     | 64G     | 256G    | 1T        |

| Wiring level            | 6       | 6-7        | 7         | 7-8     | 8–9     | 9       | 10        |

| Supply voltage          |         |            |           |         |         |         | 3         |

| (V)                     | 1.8-2.5 | 1.5 - 1.8  | 1.2 - 1.5 | 0.9-1.2 | 0.6-0.9 | 0.5-0.6 | 0.37-0.42 |

| Power (W)               | 70      | 90         | 130       | 160     | 170     | 175     | 183       |

- Source: International Technology Roadmap for Semiconductors, Nov, 2002. <u>http://www.itrs.net/ntrs/publntrs.nsf</u>

- Deep submicron technology: node (feature size) < 0.25 μm</p>

- □ Nanometer Technology: node < 0.1  $\mu m$

#### Nanometer Design Challenges

- □ In 2005, feature size  $\approx$  0.1  $\mu$ m,  $\mu$  P frequency  $\approx$  3.5 GHz, die size  $\approx$  520 mm<sup>2</sup>,  $\mu$  P transistor count per chip  $\approx$  200M, wiring level  $\approx$  8 layers, supply voltage  $\approx$  1 V, power consumption  $\approx$  160 W.

- Chip complexity

effective design and verification methodology? more efficient optimization algorithms? time-to-market?

Power consumption

power & thermal issues?

Supply voltage

signal integrity (noise, IR drop, etc)?

- Feature size, dimension

- sub-wavelength lithography (impacts of process variation)? noise? wire coupling? reliability? manufacturability? 3D layout?

Frequency

interconnect delay? electromagnetic field effects? timing closure?

#### Design Complexity Challenges

- Design issues

- Design space exploration

- More efficient optimization algorithms

- Verification issues

- State explosion problem

- For modern designs, about 60%-80% of the overall design time was spent on verification; 3-to-1 head count ratio between verification engineers and logic designers

Pentium 4

#### Semiconductor Fabrication Challenges

Feature-size shrinking approaches physical limitation

# **VLSI CAD Engineering**

#### Introduction

#### EDA, where HW and SW meet each other

#### EDA in Chip Design

#### EDA is concerned about HW/SW design in terms of

- Correctness

- Productivity

- Optimality

- Scalability

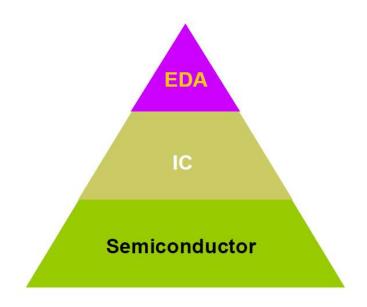

#### EDA and Industries

# EDA (in a strict sense) and industries Impact - solving a problem may benefit vast electronic designs

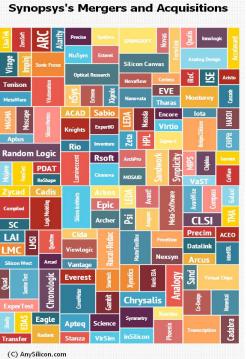

#### EDA Vendors and Tools Development

- List of EDA Companies

- EDA's big three:

- Cadence

- Synopsys

- Mentor

- EDA R&D

- Application Engineer

Lots of Mergers and Acquisitions

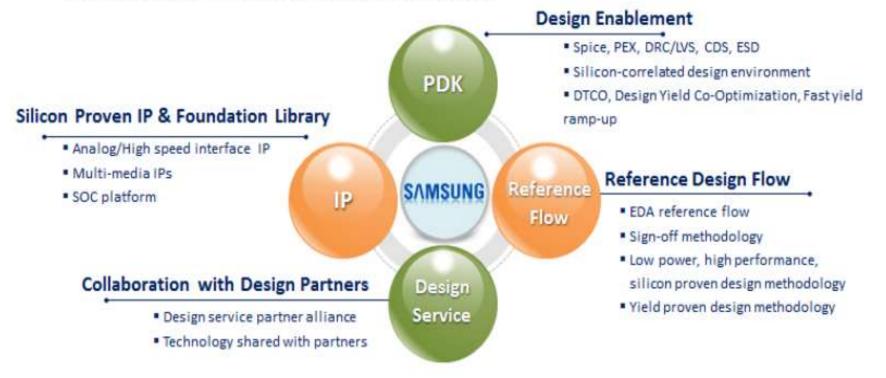

#### Foundry PDK and IP Reuse

Full spectrum of foundry design ecosystem

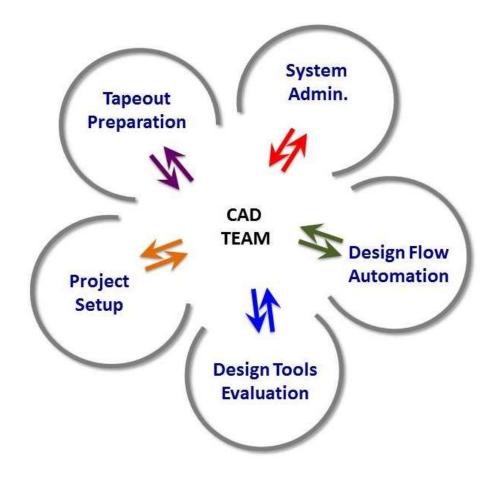

#### CAD Design Enablement

- Work with IT closely (license, network, disk space, remote site, revision control, security ...)

- With deep understanding of chip design and EDA tool capabilities make sure to set up and automate all flows running smoothly till successfully tapeout to foundry

- Interfaces between the design teams and EDA vendors to evaluate the design tools that ensure the correct tools are set up for the design project.

- Must be good at:

- Strong system admin (plus)

- Solid understanding the chip design methodology and implementation

- Excellent on programming and scripting

- Good communication Skill

#### CAD as Career

- This career field would appeal to someone who enjoys problem solving, both software and hardware and working with engineers

- Someone has creative mindset, interested in exploring problem around them and solve it

- Someone interested in new technology at all levels and wants to learn new things everyday

- Someone has great satisfaction if they create something useful, or helped someone through automation

- Someone acts as "unsung hero in a successful tapeout"

#### References

- C. (Producer). (2016, October 19). CAD innovation over the years [Video file]. Retrieved from https://www.youtube.com/watch?v=ZgQD95NhbXk

- Sunkara, V. (Producer). (2014, January 08). EDA : Where Electronics Begins [Video file]. Retrieved from https://www.youtube.com/watch?v=IAKtkgfaFzQ

- N. (2014, January 22). Zoom Into a Microchip. Retrieved from https://www.youtube.com/watch?v=Fxv3JoS1uY8

- C. (2012, May 25). Intel: The Making of a Chip with 22nm/3D Transistors | Intel. Retrieved from https://www.youtube.com/watch?v=d9SWNLZvA8g

- · Computer-aided design. (2017, August 05). Retrieved from https://en.wikipedia.org/wiki/Computer-aided\_design

- · Very-large-scale integration. (2017, July 14). Retrieved from https://en.wikipedia.org/wiki/Very-large-scale\_integration

- · Integrated circuit design. (2017, August 01). Retrieved from https://en.wikipedia.org/wiki/Integrated\_circuit\_design

- Jlang, J. R. (2014, Spring). Introduction to Electronic Design Automation. Retrieved from http://cc.ee.ntu.edu.tw/~jhjiang/instruction/courses/spring14-eda/lec01.pdf

- Tehranipoor, M. (October 7). CAD Algorithms Physical Design Automation of VLSI Systems. Retrieved 2008, from http://www.engr.uconn.edu/~tehrani/teaching/cad/11\_intro.pdf

- How do integrated circuits work? (2016, December 04). Retrieved from http://www.explainthatstuff.com/integratedcircuits.html

- Cadence Mergers and Acquisitions [infographic]. (2013, September 05). Retrieved from http://anysilicon.com/cadence-mergers-and-acquisitions-historyinfographic/

- Synopsys Mergers and Acquisitions infographic. (2013, September 09). Retrieved from http://anysilicon.com/synopsys-mergers-acquisitions-history-infographic/

- · List of EDA companies. (2017, August 03). Retrieved from https://en.wikipedia.org/wiki/List\_of\_EDA\_companies

- Gary Smith EDA » Atoptech Shows Explosive Growth. (2011, November). Retrieved from https://www.garysmitheda.com/2011/01/atoptech-shows-explosive-growth/

- Varde, A. (2014, March 14). The CAD Team Unsung heroes in a successful tapeout. Retrieved from https://www10.edacafe.com/blogs/guest/2014/03/14/the-cad-team-unsung-heroes-in-a-successful-tapeout/

- Low, K. (2016, April 20). A Look at Samsung Foundry's Business Strategy, Manufacturing Excellence and Advanced Technology Updates. Retrieved from

https://www.samsungsemiblog.com/foundry/a-look-at-samsung-foundrys-business-strategy-manufacturing-excellence-and-advanced-technology-updates/

#### Appendix: Milestones of IC Industry

- **1947:** Bardeen, Brattain & Shockly invented the transistor, foundation of the IC industry.

- **1952:** SONY introduced the first transistor-based radio.

- **1958:** Kilby invented integrated circuits (ICs).

- **1965:** Moore's law.

- **1968:** Noyce and Moore founded Intel.

- **1970:** Intel introduced 1 K DRAM.

Shockley and Walter Brattain shared the Nobel Prize in Physics for their discovery of the transistor.

Carting OLLETSE BERGE

First transistor

First IC by Noyce

#### Appendix: Milestones of IC Industry (cont'd)

- 1971: Intel announced 4-bit 4004 microprocessors (2250 transistors).

- **1976/81:** Apple II/IBM PC.

- **1985:** Intel began focusing on microprocessor products.

- **1987:** TSMC was founded (fabless IC design).

- **1991:** ARM introduced its first embeddable RISC IP core (chipless IC design).

Intel founders

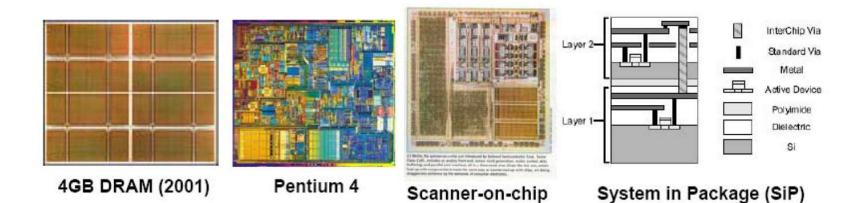

#### Appendix: Milestones of IC Industry (cont'd)

- **1996:** Samsung introduced 1G DRAM.

- **1998:** IBM announces 1GHz experimental microprocessor.

- **1999/earlier: System-on-Chip (SoC)** methodology applications.

- 2002/earlier: System-in-Package (SiP) technology

- An Intel P4 processor contains 42 million transistors (1 billion by 2005)

- Today, we produce > 1 billion transistors per person.

#### Q&A